Static random-access memories (SRAM) based FPGAs are susceptible to Single Event Upsets (SEUs). SEUs are transient faults caused by high-energy particles striking the semiconductor material which result in unintended changes in the stored data. This vulnerability is a significant concern specifically in environments with high levels of radiation, such as outer space or near nuclear reactors, where particle interference is more probable.

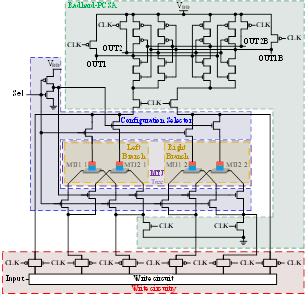

GW researchers have developed a novel SEU-hardened multi-context spintronic FPGA architecture. By integrating Magnetic Tunnel Junction (MTJ) technology as a nonvolatile memory storage, this design offers a dual advantage of storing multiple configurations internally while ensuring resilience against SEU without significant area overhead or power consumption. This approach effectively eliminates the need for external nonvolatile memory which reduces power consumption and enhances the system's performance and reliability.

Fig. Proposed SEU-hardened multi-context MRAM circuit

Advantages:

- Eliminates the need for external nonvolatile memory.

- 23% lower average power and 14% lower static power consumption compared to existing designs.

- Efficient area usage

Applications:

- Can be used in environments susceptible to radiation-induced errors.

- Machine learning and video processing.

- Multi-context applications.